The machine instruction cycle: Difference between revisions

Mr. MacKenty (talk | contribs) |

Mr. MacKenty (talk | contribs) |

||

| Line 33: | Line 33: | ||

=== 1. Fetch === | === 1. Fetch === | ||

The | The Control Unit (CU) initiates the fetch stage by using the **Program Counter (PC)** to store the address of the next instruction to be executed. This address is sent to the Memory Address Register (MAR), which holds the address of the required instruction in memory. | ||

* The CU signals the memory to retrieve the instruction at the address in the MAR. | |||

* The retrieved instruction is temporarily stored in the **Memory Data Register (MDR)**. | |||

* The instruction is then transferred to the **Current Instruction Register (CIR)** for decoding. | |||

* The PC is incremented to point to the address of the next instruction in RAM. | |||

=== 2. Decode === | === 2. Decode === | ||

Revision as of 11:13, 11 September 2024

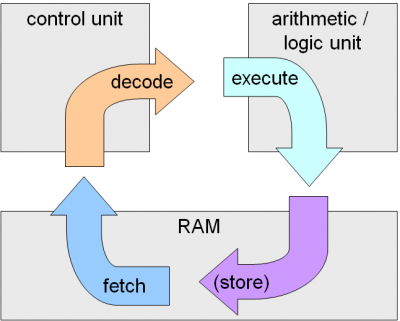

The machine instruction cycle describes the order that instructions are processed in a computer.

Instructions are processed under the direction of the control unit in a step-by-step manner.

There are four fundamental steps in the instruction cycle:

1. Fetch the instruction The next instruction is fetched from the memory address that is currently stored in the Program Counter (PC), and stored in the Instruction register (IR). At the end of the fetch operation, the PC points to the next instruction that will be read at the next cycle.

2. Decode the instruction The control unit interprets the instruction. During this cycle the instruction inside the IR (instruction register) gets decoded.

3. Execute The Control Unit of CPU passes the decoded information as a sequence of control signals to the relevant function units of the CPU to perform the actions required by the instruction such as reading values from registers, passing them to the ALU to perform mathematical or logic functions on them, and writing the result back to a register. If the ALU is involved, it sends a condition signal back to the CU.

4. Store result The result generated by the operation is stored in the main memory, or sent to an output device. Based on the condition of any feedback from the ALU, Program Counter may be updated to a different address from which the next instruction will be fetched.

Data Bus: A data bus is a connection between the different parts of a computer that information is sent on.

Address Bus: The address bus is a data bus that is used to specify a physical address. A CPU will specify the memory location.[1]

The **machine instruction cycle** is the process a CPU follows to execute instructions stored in memory. It consists of four main stages: Fetch, Decode, Execute, and Store. Below is a breakdown of the cycle, along with the roles of key components such as the Control Unit (CU), Arithmetic Logic Unit (ALU), and various registers.

1. Fetch[edit]

The Control Unit (CU) initiates the fetch stage by using the **Program Counter (PC)** to store the address of the next instruction to be executed. This address is sent to the Memory Address Register (MAR), which holds the address of the required instruction in memory.

- The CU signals the memory to retrieve the instruction at the address in the MAR.

- The retrieved instruction is temporarily stored in the **Memory Data Register (MDR)**.

- The instruction is then transferred to the **Current Instruction Register (CIR)** for decoding.

- The PC is incremented to point to the address of the next instruction in RAM.

2. Decode[edit]

Once the instruction is in the **CIR**, the **Control Unit (CU)** decodes it to determine what operation needs to be performed. The decoded instruction identifies whether data needs to be retrieved, stored, or manipulated.

3. Execute[edit]

The **Arithmetic Logic Unit (ALU)** performs the necessary calculations or logical operations, depending on the instruction. For example, if the instruction involves an arithmetic operation (addition, subtraction, etc.), the ALU processes the data.

- Data required for the operation may be fetched from memory or registers. - The **Accumulator (ACC)** stores the result of operations carried out by the ALU, such as the sum of two numbers.

4. Store[edit]

After execution, the result in the **ACC** may need to be stored back into memory or passed to another register for further operations. If the instruction involves interacting with external devices, the **Interrupt Register (IR)** may be involved, handling requests from I/O devices to ensure they are serviced when required.

During the entire instruction cycle, the **Control Unit (CU)** coordinates the movement of data between the registers and manages the flow of control within the CPU.

Registers' Summary[edit]

PC (Program Counter): Stores the address of the next instruction to be fetched. MAR (Memory Address Register): Stores the memory address of the data or instruction to be fetched or stored. MDR (Memory Data Register): Holds the data fetched from or to be written to memory. CIR (Current Instruction Register): Stores the current instruction being decoded and executed. ACC (Accumulator): Holds the result of calculations performed by the ALU. IR (Interrupt Register): Manages interrupt requests from I/O devices.

The cycle then repeats, fetching the next instruction from memory as indicated by the Program Counter (PC).

Excellent simulations of the machine instruction cycle[edit]

- It can be helpful to imagine there is a little mailman inside your computer! Click here to learn more about this technique

- Click here for a great simulation!

- This is also very good simulation (little man simulation)